Signal and Power integrity analysis

Signal and Power Integrity (SI/PI) analysis plays essential role for today’s ever increasing high-speed designs. SI/PI analysis helps to identify the problems early in the design phase that enable us to avoid re-spins and longer time to market. In Today’s competitive world, you have to reduce Time to Market (TTM) to gain your edge over competitors.

How Wavetroniks can help you?

Our team has extensive experience with high-speed system design such as 56G PAM4, 28Gbps NRZ, PCIe Gen-3/4, SAS-3/12Gbps, (DDR3/4) etc.

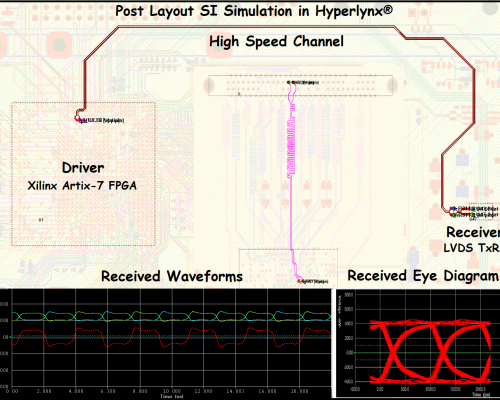

Our highly experienced SI team can solve the toughest problems, compliments with the best available tools that we use i.e. Mentor Graphics HyperLynx®, ANSYS HFSS™, Cadence® Allegro PCB SI, Synopsys HSPICE® and Polar Instruments Si9000®.

Signal Integrity Highlights

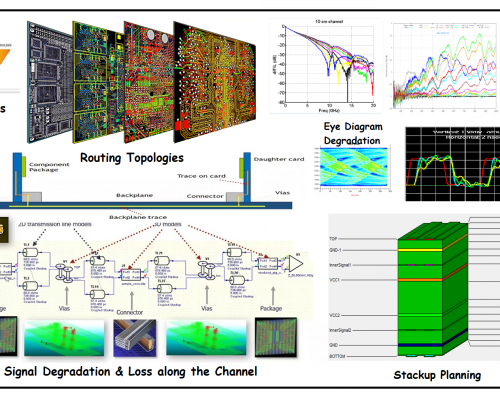

- Pre-Layout and Post Layout Signal Integrity & Constraints Generation

- IBIS, SPICE & S-Parameter Simulations

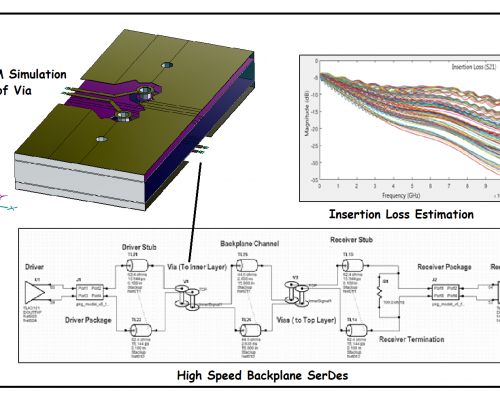

- 2D/3D- Electromagnetic Simulation

- IBIS-AMI Simulation of High Speed SerDes

- Channel Eye Diagram Extraction & Analysis

- Signal Integrity Driven Stackup Planning

- Net scheduling and design optimization for complex topologies like multi-drop buses (DDR3, DDR4)

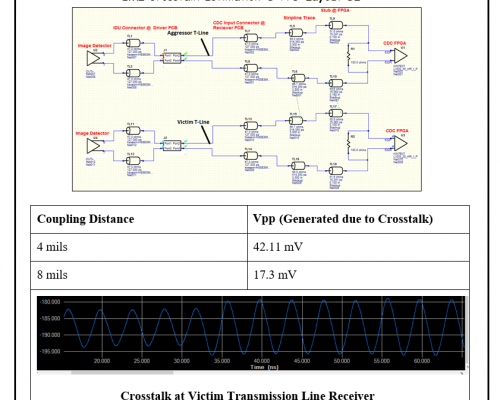

- Crosstalk, Electromagnetic Compatibility

- TDR/TDT Analysis of High Speed SerDes

- Pre-Emphasis & Equalization of High Speed SerDes

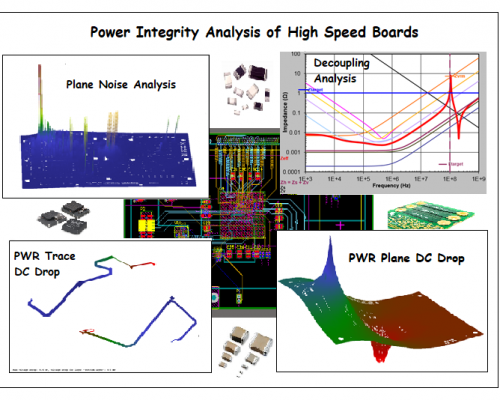

Power Integrity Highlights

- Pre-Layout and Post Layout Power Integrity & Constraints Generation

- Power Delivery Network Design (PDN) & Analysis

- Component & system characterization, including full S-parameters, gain and noise figure optimization

- Power Integrity Aware Stackup Planning

- Power/Ground Plan Decoupling Analysis

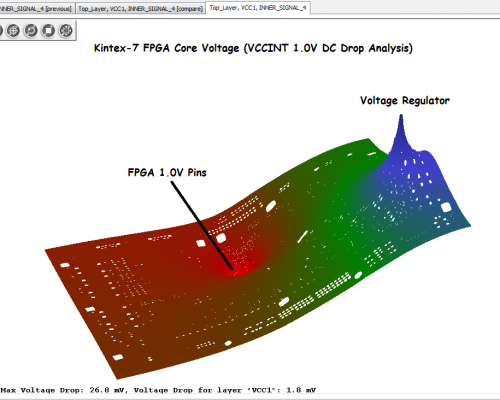

- Plan AC/DC Drop Analysis

- Power Plan Noise Analysis

Tools Set

- Signal & Power Integrity

- Mentor Graphics® HyperLynx® SI/PI & 3D EM

- ANSYS HFSS & SI Wave™

- Synopsys HSPICE®

- Polar Instruments Si9000® etc.

- Analog Devices LTspice